## COE211: Digital Logic Design

#### Synchronous Sequential Logic Part 2: Sequential Circuits Analysis and Design

### Analysis of Sequential Circuits

- Behavior of clocked sequential circuit determined by

- Inputs

- Outputs

- State of flip-flops

- Analysis process

- Consider all combinations of

- Inputs

- Flip-flop states

- Determine next state and output of circuit

- Concept of a Finite State Machine (FSM)

- Methods

- State equations

- State table

- State diagram

10/22/2022

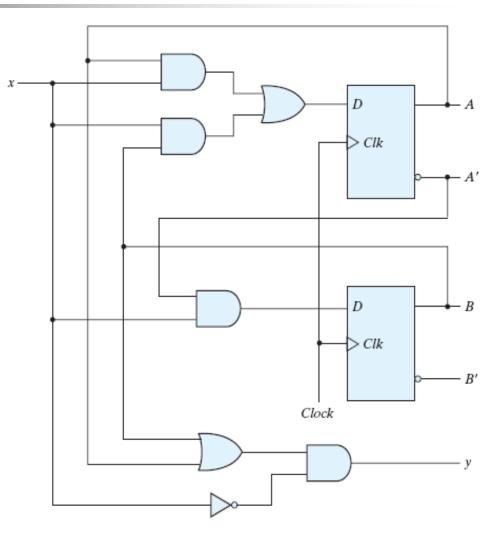

#### **Example Circuit**

- Sequential circuit

- Input: x

- Output: y

- Flip-flops:

- 2 D-type FFsA and B

- When is y=1?

- Very difficult to answer

- Systematic analysis necessary

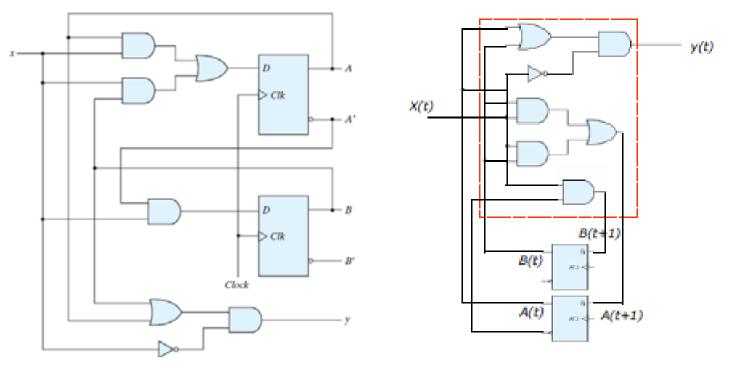

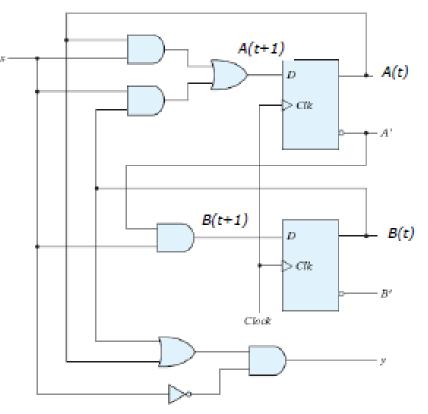

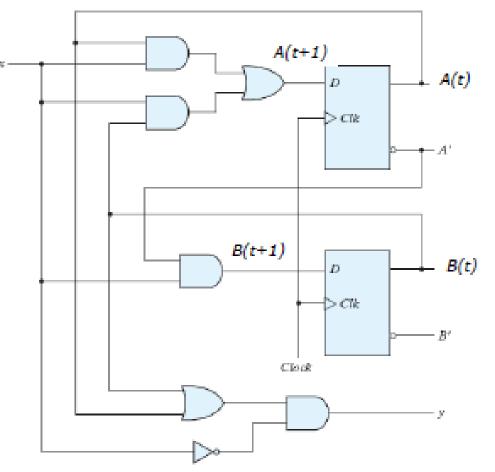

### State and Output Equations

Circuit view

FSM view

A(t+1) = A(t) x(t) + B(t) x(t) B(t+1) = A'(t) x(t)y(t) = (A(t) + B(t)) x'(t)

COE211: Digital Logic Design

#### State and Output Equations

- State equation specifies next state

- Function of current state and inputs

- State equation for flip-flops:

- A(t+1) = A(t) x(t) + B(t) x(t)

- B(t+1) = A'(t) x(t)

- Output expression:

- y(t) = (A(t) + B(t)) x'(t)

- Simplified notation:

- A(t+1) = A x + B x

- B(t+1) = A' x

- y = (A+B) x'

- How to derive these Eqs?

### Flip-flop Input Equations

- Similar to state equations

- Specifies type of flip-flop used

- In case of D-FFs

they are the

same as state equations.

- This circuit:

- DA = A x + B x

- DB = A' x

- y = (A + B) x'

# State Table

- What needs to be considered in table?

- Inputs

- State of flip-flops

- Next state of flip-flops

- Outputs

- How many entries in state table?

- n inputs

- m number of flip-flops

- Total of 2<sup>m+n</sup> entries

- For every entry

- Determine flip-flop change by input and current state

- State equation

- Determine the output (Output equation)

|   | sent<br>ate | Input |   | ext<br>ate | Output |

|---|-------------|-------|---|------------|--------|

| A | В           | x     | A | B          | У      |

| 0 | 0           | 0     | 0 | 0          | 0      |

| 0 | 0           | 1     | 0 | 1          | 0      |

| 0 | 1           | 0     | 0 | 0          | 1      |

| 0 | 1           | 1     | 1 | 1          | 0      |

| 1 | 0           | 0     | 0 | 0          | 1      |

| 1 | 0           | 1     | 1 | 0          | 0      |

| 1 | 1           | 0     | 0 | 0          | 1      |

| 1 | 1           | 1     | 1 | 0          | 0      |

Copyright ©2012 Pearson Education, publishing as Prentice Hall

#### COE211: Digital Logic Design

#### **Table 5.3** Second Form of the State Table

| Present<br>State |   | <b>Next State</b>   |   |              |   | Output |              |  |

|------------------|---|---------------------|---|--------------|---|--------|--------------|--|

|                  |   | <i>x</i> = <b>0</b> |   | <i>x</i> = 1 |   | x = 0  | <i>x</i> = 1 |  |

| Α                | В | A                   | B | Α            | B | у      | y            |  |

| 0                | 0 | 0                   | 0 | 0            | 1 | 0      | 0            |  |

| 0                | 1 | 0                   | 0 | 1            | 1 | 1      | 0            |  |

| 1                | 0 | 0                   | 0 | 1            | 0 | 1      | 0            |  |

| 1                | 1 | 0                   | 0 | 1            | 0 | 1      | 0            |  |

Copyright ©2012 Pearson Education, publishing as Prentice Hall

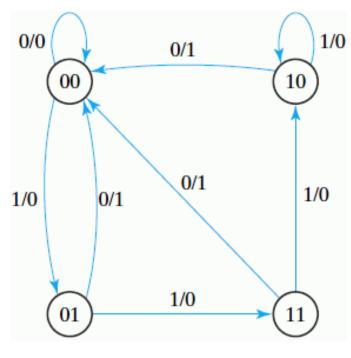

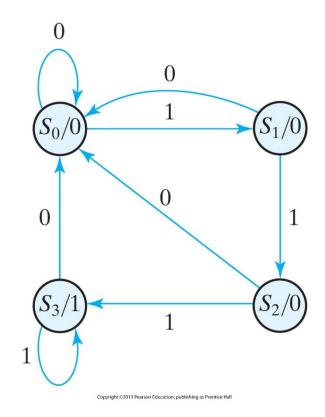

- State transitions represented as graph

- Vertices indicate states

- Edges represent transitions

- Edge annotation: "x/y" meaning input is x and output is y

|   | sent<br>ate | Input |   | ext<br>ate | Output |  |  |

|---|-------------|-------|---|------------|--------|--|--|

| Α | В           | x     | A | B          | Y      |  |  |

| 0 | 0           | 0     | 0 | 0          | 0      |  |  |

| 0 | 0           | 1     | 0 | 1          | 0      |  |  |

| 0 | 1           | 0     | 0 | 0          | 1      |  |  |

| 0 | 1           | 1     | 1 | 1          | 0      |  |  |

| 1 | 0           | 0     | 0 | 0          | 1      |  |  |

| 1 | 0           | 1     | 1 | 0          | 0      |  |  |

| 1 | 1           | 0     | 0 | 0          | 1      |  |  |

| 1 | 1           | 1     | 1 | 0          | 0      |  |  |

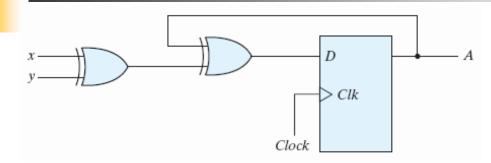

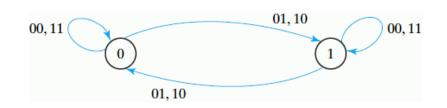

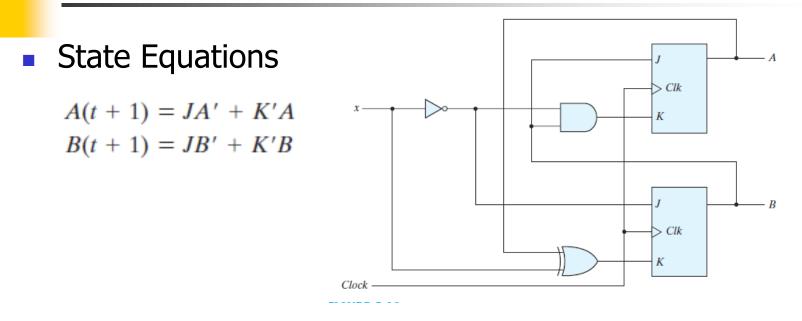

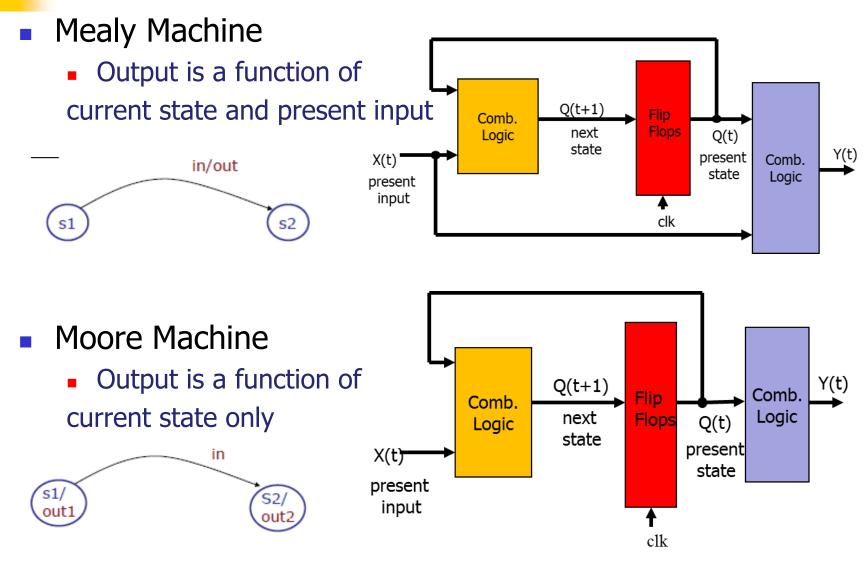

### Analysis Example 2

Equation:

$\begin{array}{l} A(t+1) = A \oplus_X \oplus_Y & (\text{state equation}) \\ D_A(t+1) = A \oplus_X \oplus_Y & (\text{flip-flop equation}) \end{array}$

Next

Present

- State table:

- State diagram:

- Note: no outputs

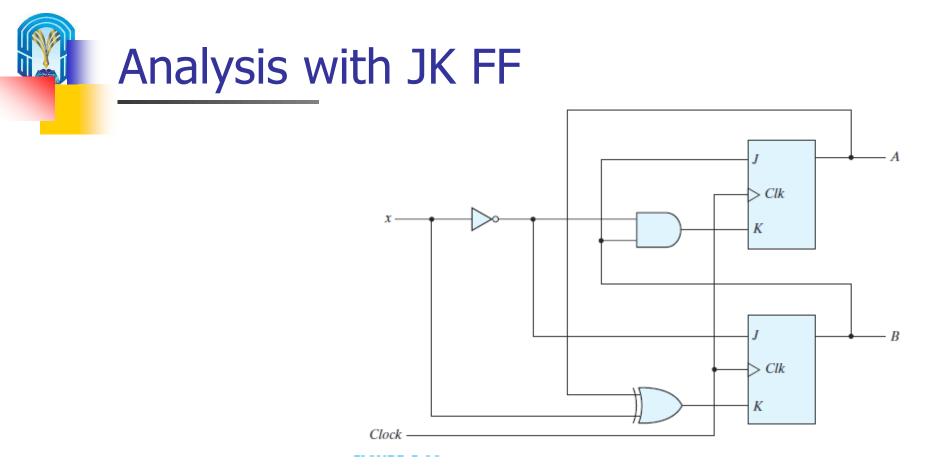

Flip-flop Input Equations  $J_A = B$   $K_A = Bx'$  $J_B = x'$   $K_B = A'x + Ax' = A \oplus x$

### Analysis with JK FF

$$J_A = B \quad K_A = Bx'$$

$$J_B = x' \quad K_B = A'x + Ax' = A \oplus x$$

A(t+1) = BA' + (Bx')'A = A'B + AB' + Ax $B(t+1) = x'B' + (A \oplus x)'B = B'x' + ABx + A'Bx'$

#### Analysis with JK FF

State Equations

A(t + 1) = BA' + (Bx')'A = A'B + AB' + Ax

$B(t + 1) = x'B' + (A \oplus x)'B = B'x' + ABx + A'Bx'$

- State table:

- State Diagram:

#### State Table for Sequential Circuit with JK Flip-Flops

|   | sent<br>ate | Input | Next<br>State |   | Flip-Flop<br>Inputs |                |                |                |

|---|-------------|-------|---------------|---|---------------------|----------------|----------------|----------------|

| Α | В           | x     | Α             | В | JA                  | K <sub>A</sub> | J <sub>B</sub> | K <sub>B</sub> |

| 0 | 0           | 0     | 0             | 1 | 0                   | 0              | 1              | 0              |

| 0 | 0           | 1     | 0             | 0 | 0                   | 0              | 0              | 1              |

| 0 | 1           | 0     | 1             | 1 | 1                   | 1              | 1              | 0              |

| 0 | 1           | 1     | 1             | 0 | 1                   | 0              | 0              | 1              |

| 1 | 0           | 0     | 1             | 1 | 0                   | 0              | 1              | 1              |

| 1 | 0           | 1     | 1             | 0 | 0                   | 0              | 0              | 0              |

| 1 | 1           | 0     | 0             | 0 | 1                   | 1              | 1              | 1              |

| 1 | 1           | 1     | 1             | 1 | 1                   | 0              | 0              | 0              |

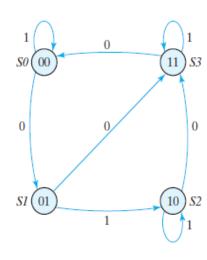

#### Finite State Machines

- State diagrams are representations of Finite State Machines (FSM)

- Two flavors of FSMs:

- Mealy FSM

- Moore FSM

- Difference:

- How output is determined

- Mealy FSM

- Output depends on input and state

- Output is not synchronized with clock

- can have temporarily unstable output

- Moore FSM

- Output depends only on state

s1

s1/

out1

in/out

in

s2

S2/

#### Mealy vs Moore Machine

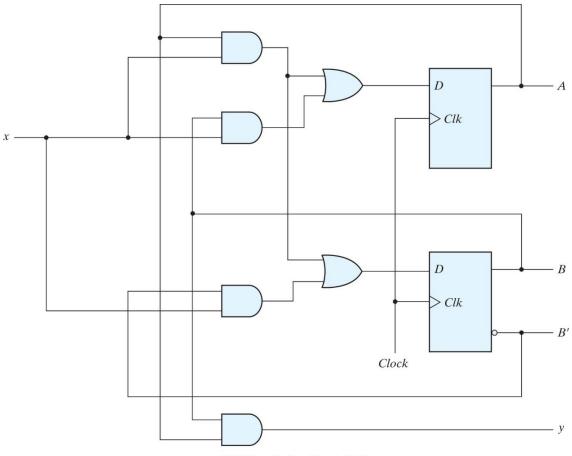

#### **Design of Sequential Circuits**

## Design of Sequential Circuits

- Derive state diagram from description

Reduce number of states if necessary (will NOT be covered)

- 2. Assign binary values to states

- 3. Obtain binary coded state table (transition table)

- 4. Choose type of flip-flops

- 5. Derive flip-flop input equations and output equations

- 6. Draw logic diagram

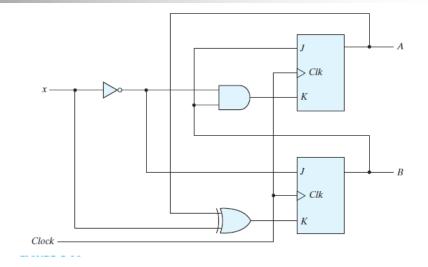

#### Example 1: Sequence Detector

- Circuit specification:

- Design a circuit that outputs a 1 when three consecutive 1s have been applied to input, and 0 otherwise."

- Step 1: derive state diagram

- What should a state represent?

- E.g., "number of 1's seen so far"

- Moore or Mealy FSM?

- Both possible

- Chose Moore to simplify diagram

- State diagram:

- State S0: zero 1s detected

- State S1: one 1 detected

- State S2: two 1s detected

- State S3: three 1s detected

#### **Example 1: Sequence Detector**

Present

State

A

0

()

0

0

1

1

Characteristic equation: Q(t+1)=DQ

B

0

0

- Step 2: state assignment

- Two flip-flops

- Binary state coding

Input

X

0

1

- Step 3: Binary coded state table

- Name flip-flops A and B

- Step 4: Choose type of flip-flops

- E.g., D flip-flop

1 0 0 0 ()1 1 1 0 () 0 ()()()()0 1 1 () 0 0 0 1 1 1 1 1

Next

State

A

0

0

B

0

1

Copyright ©2012 Pearson Education, publishing as Prentice Hall

Output

Y

0

()

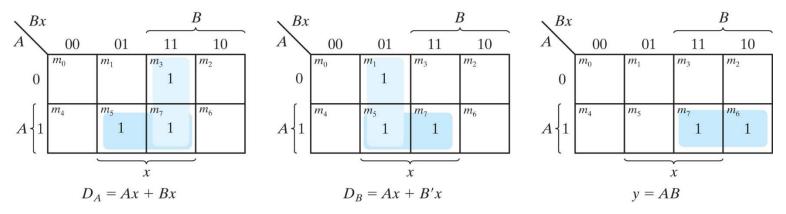

- Step 6: derive flip-flop input equations and output equation

- Use state table

$$A(t+1) = D_A(A,B,x)$$

=  $\Sigma(3,5,7)$

$$\begin{split} B(t+1) &= D_B(A,B,x) \\ &= \mathcal{L}(1,5,7) \end{split}$$

$\begin{array}{l} y(A,B,x)=\varSigma(6,7)\\ or\ y(A,B)=\varSigma(3) \end{array}$

Table 5.11State Table for Sequence Detector

| Present<br>State |   | Input | Ne<br>Sta | xt<br>ate | Output |  |

|------------------|---|-------|-----------|-----------|--------|--|

| A                | В | x     | A         | В         | У      |  |

| 0                | 0 | 0     | 0         | 0         | 0      |  |

| 0                | 0 | 1     | 0         | 1         | 0      |  |

| 0                | 1 | 0     | 0         | 0         | 0      |  |

| 0                | 1 | 1     | 1         | 0         | 0      |  |

| 1                | 0 | 0     | 0         | 0         | 0      |  |

| 1                | 0 | 1     | 1         | 1         | 0      |  |

| 1                | 1 | 0     | 0         | 0         | 1      |  |

| 1                | 1 | 1     | 1         | 1         | 1      |  |

Copyright ©2012 Pearson Education, publishing as Prentice Hall

• Step 6b: minimize equations  $A(t+1) = \Sigma(3,5,7)$   $B(t+1) = \Sigma(1,5,7)$  $y(A,B) = \Sigma(3) - easy: y = AB$

Copyright ©2013 Pearson Education, publishing as Prentice Hall

#### COE211: Digital Logic Design

# Example 1: Sequence Detector

Copyright ©2013 Pearson Education, publishing as Prentice Hall

#### COE211: Digital Logic Design

- Flip flops contain state information

- State can be represented in several forms:

- State equations

- State table

- State diagram

- Possible to convert between these forms

- Circuits with states can take on a finite set of values

- Finite state machine

- Two types of "machines"

- Mealy machine

- Moore machine